Bài viết này tập trung vào giải thích, phân tích các bước trong design flow của Openlane2. Tất cả thông tin ở đây là “ý kiến cá nhân”, không dựa vào tài liệu hướng dẫn nào của Openlane2. Một số thông tin chưa được làm rõ, chưa được tìm hiểu sâu. Một số thuật ngữ được dùng lộn xộn giữa tiếng Anh và Tiếng Việt, mong anh em thông cảm.

Dưới đây là các bước trong quy trình của 1 project đầy đủ. Giải thích chi tiết sẽ cập nhật từ từ nhé.

—————————————————————————————–

01-verilator-lint:

Bước này kiểm tra toàn bộ code RTL của thiết kế. Các nội dung kiểm tra có thể bao gồm:

– Cú pháp của câu lệnh trong code (syntax Error)

– Các từ khóa ko được sử dụng

– Quy tắc sử dụng các loại tín hiệu và các toán tử của chúng

– Quy tắc sử dụng các cú pháp coding cho từng loại biến

– Các lỗi có thể gây ra trở ngại trong các bước tiếp theo (Synthesis chẳng hạn..)

– Các cảnh báo (Warning) về các quy tắc của Verilog khác

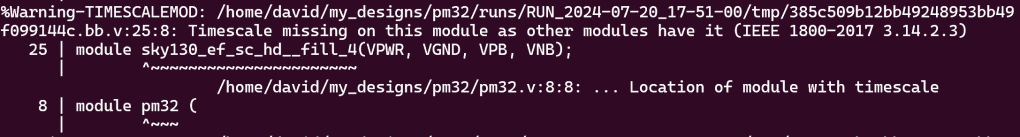

Ví dụ 1:

Đây là cảnh báo về một module ko khai báo “timescale” trong khi những module khác đã có khai báo. Đây là rule dựa trên tiêu chuẩn IEEE 1800-2017, 3.2.14.2.4=3.

Tại sao lại có cảnh báo này ? Khi tool đọc thiết kế vào, nó phải có cách chọn timescale cho tất cả các modules. Điều này là vì trong thực tế, tool sẽ có mặc định cho timescale, user có thể define lại, và tool mong đợi nếu có thì tất cả module nên có cùng nhau. Do đó, khi phát hiện 1 module không có timescale, tool sẽ đưa ra cảnh báo để user review lại phần timescale, có cần thiết phải thay đổi, hoặc chỉnh sửa không ?

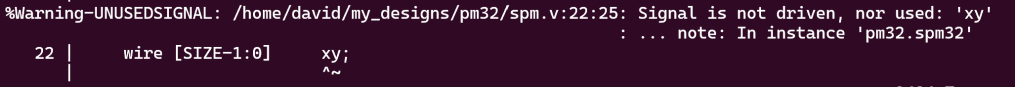

Ví dụ 2:

Đây là cảnh báo về một tín hiệu được khai báo, nhưng không được sử dụng. Vì sao Tool nó báo ra cảnh báo này ? User có thể đã quên không sử dụng tín hiệu này, hoặc sau khi cân nhắc không dùng nữa, user quên không bỏ đi. User nên kiểm tra lại code, xóa tín hiệu này đi, hoặc sữa lại phần code bị thiếu liên quan đến tín hiệu này.

02-checker-linttimingconstructs

03-checker-linterrors

04-checker-lintwarnings

– Các bước kiểm tra (checker) cần thiết trước khi đưa vào bước Synthesis – chưa có phần thiết kế cụ thể để minh họa.

05-yosys-jsonheader

Đây là phần Pre-Work của Synthesis. Chuẩn bị các input cho phần synthesis.

5. Executing PROC pass (convert processes to netlists).

– Tool sẽ chuyển đổi thông tin của design sang thông tin của thư viện bao gồm cell, IO, RAM, ROM, IP… Netlist là design ở dạng kết nối các cổng và thành phần của library, thay vì là RTL code.

5.1. Executing PROC_CLEAN pass (remove empty switches from decision trees).

5.2. Executing PROC_RMDEAD pass (remove dead branches from decision trees).

5.3. Executing PROC_PRUNE pass (remove redundant assignments in processes).

5.4. Executing PROC_INIT pass (extract init attributes).

5.5. Executing PROC_ARST pass (detect async resets in processes).

5.6. Executing PROC_ROM pass (convert switches to ROMs).

5.7. Executing PROC_MUX pass (convert decision trees to multiplexers).

5.8. Executing PROC_DLATCH pass (convert process syncs to latches).

5.9. Executing PROC_DFF pass (convert process syncs to FFs).

5.10. Executing PROC_MEMWR pass (convert process memory writes to cells).

5.11. Executing PROC_CLEAN pass (remove empty switches from decision trees).

5.12. Executing OPT_EXPR pass (perform const folding).

06-yosys-synthesis

1. Executing Liberty frontend: /home/david/.volare/volare/sky130/versions/bdc9412b3e468c102d01b7cf6337be06ec6e9c9a/sky130A/libs.ref/sky130_fd_sc_hd/lib/sky130_fd_sc_hd__tt_025C_1v80.lib

– Đọc lib từ PDK vào database.

2. Executing Verilog-2005 frontend: /home/david/my_designs/pm32/pm32.v

3. Executing Verilog-2005 frontend: /home/david/my_designs/pm32/spm.v

– Đọc verilog của design vào database

4. Executing HIERARCHY pass (managing design hierarchy).

4.1. Analyzing design hierarchy..

4.2. Executing AST frontend in derive mode using pre-parsed AST for module \spm'.

4.3. Analyzing design hierarchy..

4.4. Analyzing design hierarchy..

– Bước này có thể quản lý lại các đối tượng theo quan hệ tương ứng với hierarchy của design.

5. Generating Graphviz representation of design.

– Tạo ra dạng đồ họa/hình họa/Graphic của thiết kế

6. Executing TRIBUF pass.

7. Executing HIERARCHY pass (managing design hierarchy).

7.1. Analyzing design hierarchy..

7.2. Analyzing design hierarchy..

8. Executing PROC_CLEAN pass (remove empty switches from decision trees).

9. Executing PROC_RMDEAD pass (remove dead branches from decision trees).

11. Executing PROC_INIT pass (extract init attributes).

12. Executing PROC_ARST pass (detect async resets in processes).

13. Executing PROC_ROM pass (convert switches to ROMs).

14. Executing PROC_MUX pass (convert decision trees to multiplexers).

15. Executing PROC_DLATCH pass (convert process syncs to latches).

16. Executing PROC_DFF pass (convert process syncs to FFs).

17. Executing PROC_MEMWR pass (convert process memory writes to cells).

18. Executing PROC_CLEAN pass (remove empty switches from decision trees).

-> Một số bước thực hiện với process library. Giống bước 5.

19. Executing CHECK pass (checking for obvious problems).

20. Executing OPT_EXPR pass (perform const folding).

21. Executing FLATTEN pass (flatten design).

22. Executing OPT_EXPR pass (perform const folding).

23. Executing OPT_CLEAN pass (remove unused cells and wires).

– 8 -> 23,

24. Executing OPT pass (performing simple optimizations).

24.1. Executing OPT_EXPR pass (perform const folding).

24.10. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

24.11. Executing OPT_REDUCE pass (consolidate $mux and $reduce_ inputs).

24.12. Executing OPT_MERGE pass (detect identical cells).

24.13. Executing OPT_DFF pass (perform DFF optimizations).

24.14. Executing OPT_CLEAN pass (remove unused cells and wires).

24.15. Executing OPT_EXPR pass (perform const folding).

24.16. Finished OPT passes. (There is nothing left to do.)

24.2. Executing OPT_MERGE pass (detect identical cells).

24.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

24.4. Executing OPT_REDUCE pass (consolidate $mux and $reduce_ inputs).

24.5. Executing OPT_MERGE pass (detect identical cells).

24.6. Executing OPT_DFF pass (perform DFF optimizations).

24.7. Executing OPT_CLEAN pass (remove unused cells and wires).

24.8. Executing OPT_EXPR pass (perform const folding).

24.9. Rerunning OPT passes. (Maybe there is more to do..)

Executing FSM pass (extract and optimize FSM).

25.1. Executing FSM_DETECT pass (finding FSMs in design).

25.2. Executing FSM_EXTRACT pass (extracting FSM from design).

25.3. Executing FSM_OPT pass (simple optimizations of FSMs).

25.4. Executing OPT_CLEAN pass (remove unused cells and wires).

25.5. Executing FSM_OPT pass (simple optimizations of FSMs).

25.6. Executing FSM_RECODE pass (re-assigning FSM state encoding).

25.7. Executing FSM_INFO pass (dumping all available information on FSM cells).

25.8. Executing FSM_MAP pass (mapping FSMs to basic logic).

Executing OPT pass (performing simple optimizations).

26.1. Executing OPT_EXPR pass (perform const folding).

26.10. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

26.11. Executing OPT_REDUCE pass (consolidate $mux and $reduce_ inputs).

26.12. Executing OPT_MERGE pass (detect identical cells).

26.13. Executing OPT_DFF pass (perform DFF optimizations).

26.14. Executing OPT_CLEAN pass (remove unused cells and wires).

26.15. Executing OPT_EXPR pass (perform const folding).

26.16. Rerunning OPT passes. (Maybe there is more to do..)

26.17. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

26.18. Executing OPT_REDUCE pass (consolidate $mux and $reduce_ inputs).

26.19. Executing OPT_MERGE pass (detect identical cells).

26.2. Executing OPT_MERGE pass (detect identical cells).

26.20. Executing OPT_DFF pass (perform DFF optimizations).

26.21. Executing OPT_CLEAN pass (remove unused cells and wires).

26.22. Executing OPT_EXPR pass (perform const folding).

26.23. Finished OPT passes. (There is nothing left to do.)

26.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

26.4. Executing OPT_REDUCE pass (consolidate $mux and $reduce_ inputs).

26.5. Executing OPT_MERGE pass (detect identical cells).

26.6. Executing OPT_DFF pass (perform DFF optimizations).

26.7. Executing OPT_CLEAN pass (remove unused cells and wires).

26.8. Executing OPT_EXPR pass (perform const folding).

26.9. Rerunning OPT passes. (Maybe there is more to do..)

Executing WREDUCE pass (reducing word size of cells).

Executing PEEPOPT pass (run peephole optimizers).

Executing OPT_CLEAN pass (remove unused cells and wires).

Executing ALUMACC pass (create $alu and $macc cells).

Executing SHARE pass (SAT-based resource sharing).

Executing OPT pass (performing simple optimizations).

32.1. Executing OPT_EXPR pass (perform const folding).

32.2. Executing OPT_MERGE pass (detect identical cells).

32.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

32.4. Executing OPT_REDUCE pass (consolidate $mux and $reduce_ inputs).

32.5. Executing OPT_MERGE pass (detect identical cells).

32.6. Executing OPT_DFF pass (perform DFF optimizations).

32.7. Executing OPT_CLEAN pass (remove unused cells and wires).

32.8. Executing OPT_EXPR pass (perform const folding).

32.9. Finished OPT passes. (There is nothing left to do.)

Executing MEMORY pass.

33.1. Executing OPT_MEM pass (optimize memories).

33.10. Executing MEMORY_COLLECT pass (generating $mem cells).

33.2. Executing OPT_MEM_PRIORITY pass (removing unnecessary memory write priority relations).

33.3. Executing OPT_MEM_FEEDBACK pass (finding memory read-to-write feedback paths).

33.4. Executing MEMORY_BMUX2ROM pass (converting muxes to ROMs).

33.5. Executing MEMORY_DFF pass (merging $dff cells to $memrd).

33.6. Executing OPT_CLEAN pass (remove unused cells and wires).

33.7. Executing MEMORY_SHARE pass (consolidating $memrd/$memwr cells).

33.8. Executing OPT_MEM_WIDEN pass (optimize memories where all ports are wide).

33.9. Executing OPT_CLEAN pass (remove unused cells and wires).

Executing OPT_CLEAN pass (remove unused cells and wires).

Executing OPT pass (performing simple optimizations).

35.1. Executing OPT_EXPR pass (perform const folding).

35.2. Executing OPT_MERGE pass (detect identical cells).

35.3. Executing OPT_DFF pass (perform DFF optimizations).

35.4. Executing OPT_CLEAN pass (remove unused cells and wires).

35.5. Finished fast OPT passes.

Executing MEMORY_MAP pass (converting memories to logic and flip-flops).

Executing OPT pass (performing simple optimizations).

37.1. Executing OPT_EXPR pass (perform const folding).

37.10. Finished OPT passes. (There is nothing left to do.)

37.2. Executing OPT_MERGE pass (detect identical cells).

37.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

37.4. Executing OPT_REDUCE pass (consolidate $mux and $reduce_ inputs).

37.5. Executing OPT_MERGE pass (detect identical cells).

37.6. Executing OPT_SHARE pass.

37.7. Executing OPT_DFF pass (perform DFF optimizations).

37.8. Executing OPT_CLEAN pass (remove unused cells and wires).

37.9. Executing OPT_EXPR pass (perform const folding).

Executing TECHMAP pass (map to technology primitives).

38.1. Executing Verilog-2005 frontend: /nix/store/vn1kmwhr52wisnfkmn6fk9g15p3klzs0-yosys/bin/../share/yosys/techmap.v

38.2. Continuing TECHMAP pass.

Executing OPT pass (performing simple optimizations).

39.1. Executing OPT_EXPR pass (perform const folding).

39.2. Executing OPT_MERGE pass (detect identical cells).

39.3. Executing OPT_DFF pass (perform DFF optimizations).

39.4. Executing OPT_CLEAN pass (remove unused cells and wires).

39.5. Finished fast OPT passes.

Executing ABC pass (technology mapping using ABC).

40.1. Extracting gate netlist of module \pm32' to/input.blif’..

40.1.1. Executing ABC.

40.1.2. Re-integrating ABC results.

Executing OPT pass (performing simple optimizations).

41.1. Executing OPT_EXPR pass (perform const folding).

41.2. Executing OPT_MERGE pass (detect identical cells).

41.3. Executing OPT_DFF pass (perform DFF optimizations).

41.4. Executing OPT_CLEAN pass (remove unused cells and wires).

41.5. Finished fast OPT passes.

Executing HIERARCHY pass (managing design hierarchy).

42.1. Analyzing design hierarchy..

42.2. Analyzing design hierarchy..

Printing statistics.

Executing CHECK pass (checking for obvious problems).

Generating Graphviz representation of design.

Executing OPT pass (performing simple optimizations).

46.1. Executing OPT_EXPR pass (perform const folding).

46.2. Executing OPT_MERGE pass (detect identical cells).

46.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

46.4. Executing OPT_REDUCE pass (consolidate $mux and $reduce_ inputs).

46.5. Executing OPT_MERGE pass (detect identical cells).

46.6. Executing OPT_DFF pass (perform DFF optimizations).

46.7. Executing OPT_CLEAN pass (remove unused cells and wires).

46.8. Executing OPT_EXPR pass (perform const folding).

46.9. Finished OPT passes. (There is nothing left to do.)

Executing OPT_CLEAN pass (remove unused cells and wires).

Printing statistics.

Executing TECHMAP pass (map to technology primitives).

49.1. Executing Verilog-2005 frontend: /home/david/.volare/volare/sky130/versions/bdc9412b3e468c102d01b7cf6337be06ec6e9c9a/sky130A/libs.tech/openlane/sky130_fd_sc_hd/tribuff_map.v

49.2. Continuing TECHMAP pass.

Executing SIMPLEMAP pass (map simple cells to gate primitives).

Executing TECHMAP pass (map to technology primitives).

51.1. Executing Verilog-2005 frontend: /home/david/.volare/volare/sky130/versions/bdc9412b3e468c102d01b7cf6337be06ec6e9c9a/sky130A/libs.tech/openlane/sky130_fd_sc_hd/latch_map.v

51.2. Continuing TECHMAP pass.

Executing SIMPLEMAP pass (map simple cells to gate primitives).

Executing DFFLIBMAP pass (mapping DFF cells to sequential cells from liberty file).

53.1. Executing DFFLEGALIZE pass (convert FFs to types supported by the target).

Printing statistics.

Executing ABC pass (technology mapping using ABC).

55.1. Extracting gate netlist of module \pm32' to/run/user/1001/yosys-abc-CB48hw/input.blif’..

55.1.1. Executing ABC.

55.1.2. Re-integrating ABC results.

Executing SETUNDEF pass (replace undef values with defined constants).

Executing HILOMAP pass (mapping to constant drivers).

Executing SPLITNETS pass (splitting up multi-bit signals).

Executing OPT_CLEAN pass (remove unused cells and wires).

Executing INSBUF pass (insert buffer cells for connected wires).

Executing CHECK pass (checking for obvious problems).

Printing statistics.

Executing Verilog backend.

Executing JSON backend.

07-checker-yosysunmappedcells

08-checker-yosyssynthchecks

09-openroad-checksdcfiles

10-openroad-checkmacroinstances

11-openroad-staprepnr

12-openroad-floorplan

13-odb-checkmacroantennaproperties

14-odb-setpowerconnections

15-odb-manualmacroplacement

16-openroad-cutrows

17-openroad-tapendcapinsertion

18-odb-addpdnobstructions

19-openroad-generatepdn

20-odb-removepdnobstructions

21-odb-addroutingobstructions

22-openroad-globalplacementskipio

23-openroad-ioplacement

24-odb-customioplacement

25-odb-applydeftemplate

26-openroad-globalplacement

27-odb-writeverilogheader

28-checker-powergridviolations

29-openroad-stamidpnr

30-openroad-repairdesignpostgpl

31-openroad-detailedplacement

32-openroad-cts

33-openroad-stamidpnr-1

34-openroad-resizertimingpostcts

35-openroad-stamidpnr-2

36-openroad-globalrouting

37-openroad-checkantennas

38-odb-diodesonports

40-openroad-stamidpnr-3

41-openroad-detailedrouting

42-odb-removeroutingobstructions

43-openroad-checkantennas-1

44-checker-trdrc

45-odb-reportdisconnectedpins

46-checker-disconnectedpins

47-odb-reportwirelength

48-checker-wirelength

49-openroad-fillinsertion

50-openroad-rcx

51-openroad-stapostpnr

52-openroad-irdropreport

53-magic-streamout

54-klayout-streamout

55-magic-writelef

56-odb-checkdesignantennaproperties

57-klayout-xor

58-checker-xor

59-magic-drc

60-klayout-drc

61-checker-magicdrc

62-checker-klayoutdrc

63-magic-spiceextraction

64-checker-illegaloverlap

65-netgen-lvs

66-checker-lvs

67-checker-setupviolations

68-checker-holdviolations

69-checker-maxslewviolations

70-checker-maxcapviolations

71-misc-reportmanufacturability

error.log

final

![[Học làm chip đơn giản] Cài đặt Openlane2 trong 5 phút](https://nguoilamchip.com/wp-content/uploads/2024/07/image-2.png?w=1024)

![[Infographic] – Các dạng tồn tại của Chip trong Quy trình sản xuất](https://nguoilamchip.com/wp-content/uploads/2024/05/2-1.png?w=800)

Bình luận về bài viết này